Zen 4c “Bergamo”: AMD’s 16-core CCD-module heeft slechts 9,6% meer ruimte nodig dan 8-cores

Met de eerste Zen 4c “Bergamo”-processor, die volgende week wordt verwacht, graaft AMD diep in zijn trukendoos en komt met verbazingwekkende dingen. Omdat in plaats van caches expliciet te castreren, zoals eerder werd aangenomen, opties van contractfabrikant TSMC worden geïmplementeerd die een zeer goed verpakte oplossing mogelijk maken.

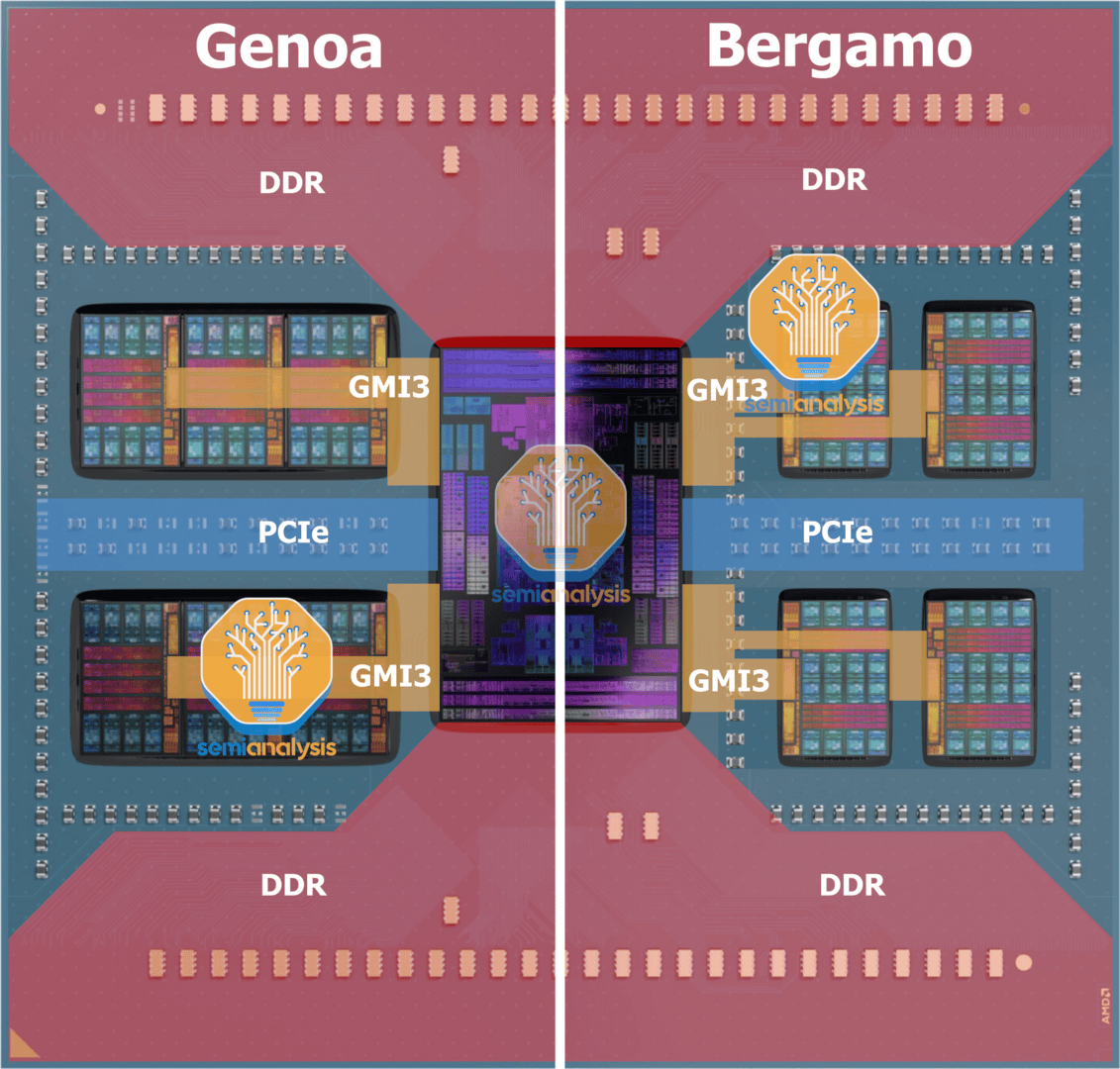

AMD comprimeert 16 cores met exact dezelfde caches in het formaat dat voorheen beschikbaar was voor 8 cores. Het enige waar het niet mee groeit, is de L3-cache, die 32 MB in CCD blijft – het is hier in feite de helft per kern. Aangezien AMD aan het einde echter 33 procent meer cores in de processor stopt, zakt de L3-cache slechts van 384 MB met Genoa met 96 cores naar 256 MB L3-cache met Bergamo en 128 cores.

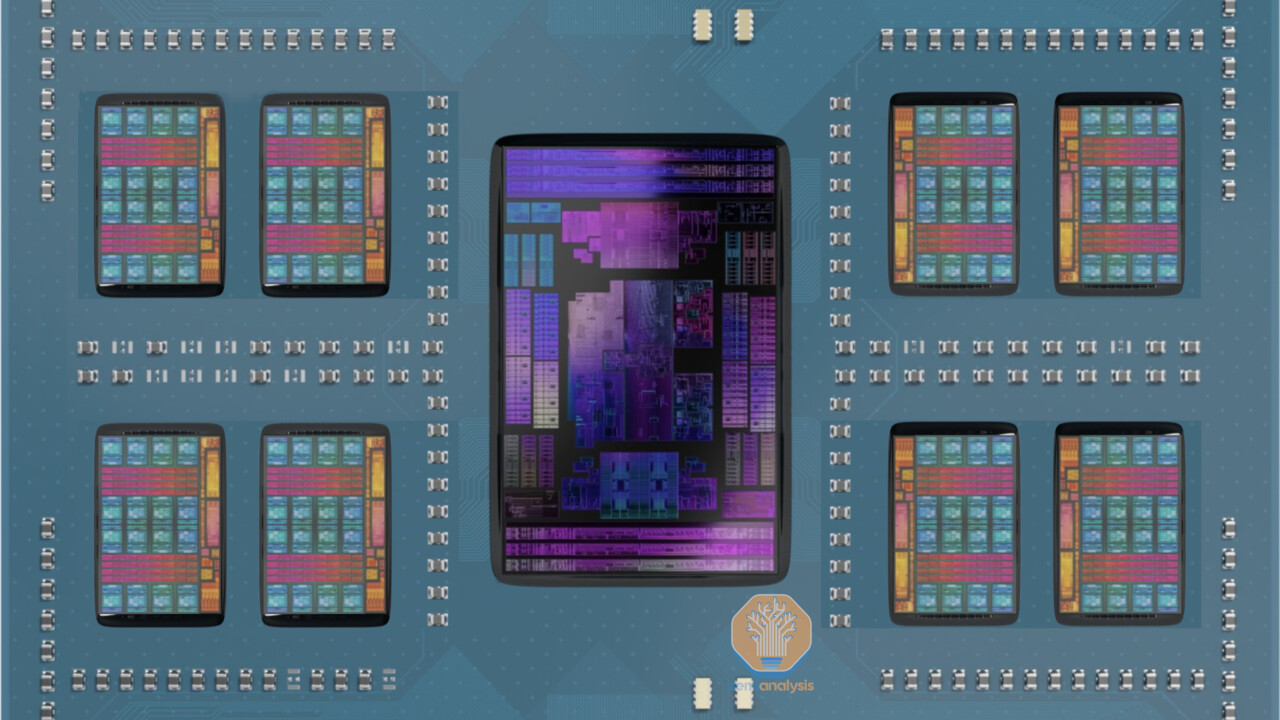

Het feit dat 16 kernen en 32 MB L3-cache in Bergamo 72,7 mm² in beslag nemen, is nogal verrassend, aangezien AMD eigenlijk 66,3 mm² specificeerde voor acht kernen en 32 MB L3-cache. Dit wordt bereikt in dezelfde N5-productie, waar gelijk nooit hetzelfde is. Omdat er enkele optimalisaties zijn die dit in de eerste plaats mogelijk maken. Maar ook hier en daar een compromis, bijvoorbeeld TSV’s, die in het vorige Zen 4-ontwerp altijd in de gestapelde L3-cache waren ingebouwd. Dat zou in Bergamo niet gebeuren, maar het maakt integendeel ruimte vrij.

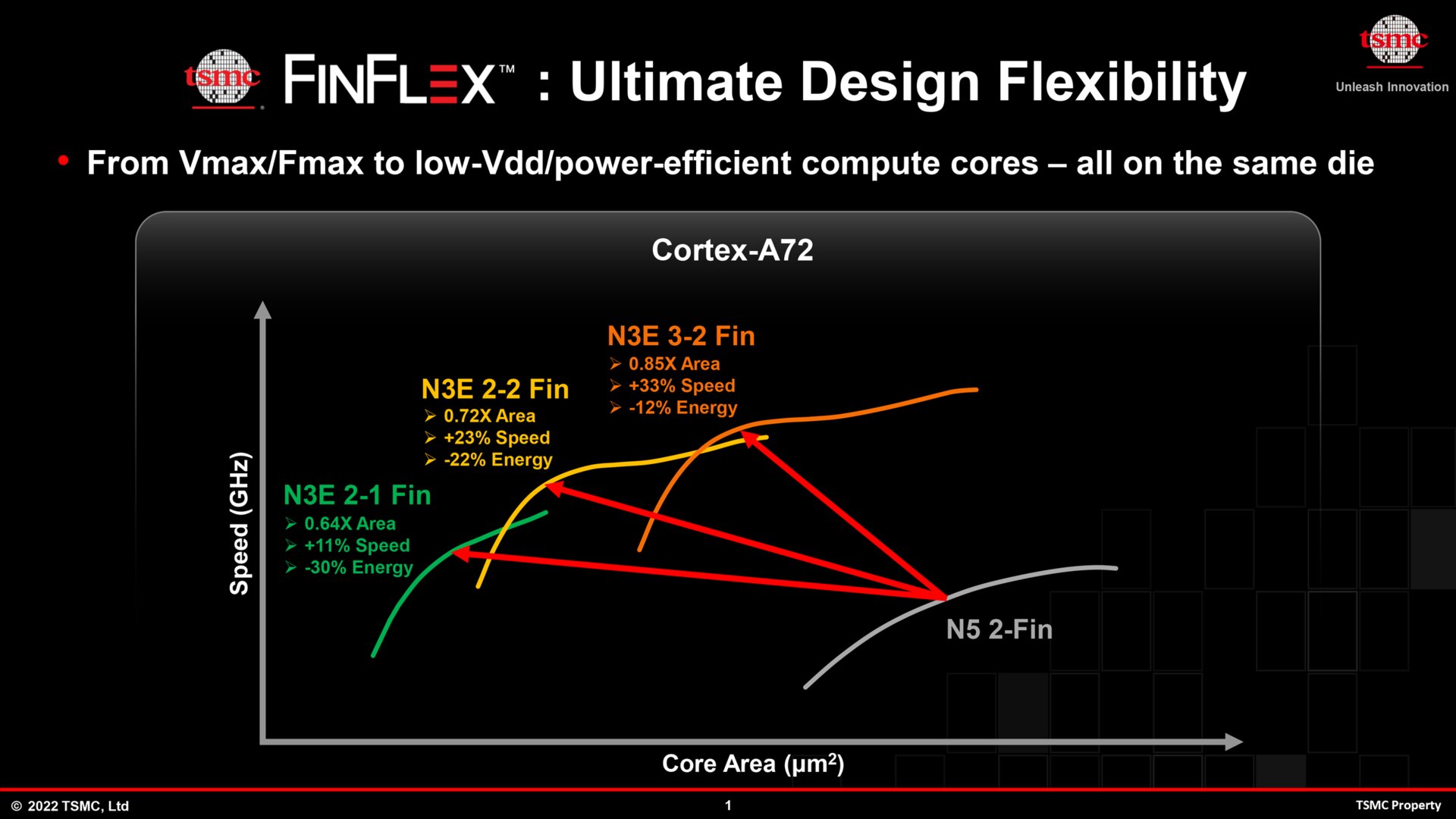

De mogelijkheden om een chip kleiner te maken en alles strakker te verpakken zijn beperkt, maar ze zijn er wel. De eerste is om de chip niet te hoog te laten klokken – dit is precies wat onder andere in Bergamo wordt gebruikt. TSMC richtte zich hierop bij de introductie van de vijf N3-technologieën, maar de grafiek laat ook op de N5-curve zien dat er altijd een keuze is tussen meer vermogen of een veel kleiner oppervlak. De betreffende lijnen komen overeen met punten die TSMC ook adresseert, zelfs de N5 kan hier veel kleiner zijn dan een ander N5-product zonder veel snelheid te verliezen.

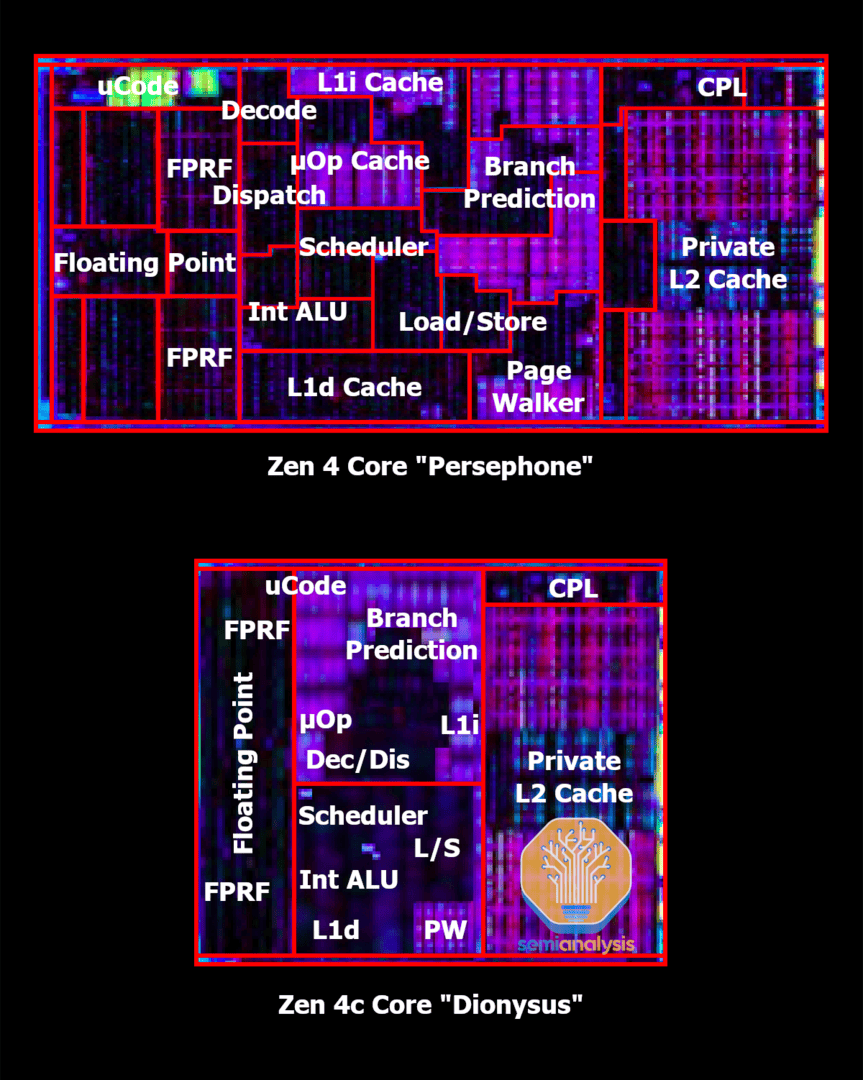

Maar dat alleen is niet genoeg: de eigenlijke kern is volledig opnieuw ontworpen en alle dingen erin zijn opnieuw gerangschikt. In plaats van er wat slordig uit te zien, is de kern nu ontworpen om meer lineair te zijn. Als we naar de grafiek kijken, is de kernruimte, inclusief de L2-cache, bijna gehalveerd. Als je het in detail bekijkt, is er een min-ratio van ongeveer 35 procent, maar sommige delen zijn qua oppervlakte al gehalveerd. Het gebruik van nieuwe, veel kleinere 6T SRAM-cellen in plaats van de 8T helpt hier ook – en die ontwikkeling is te danken aan TSMC.

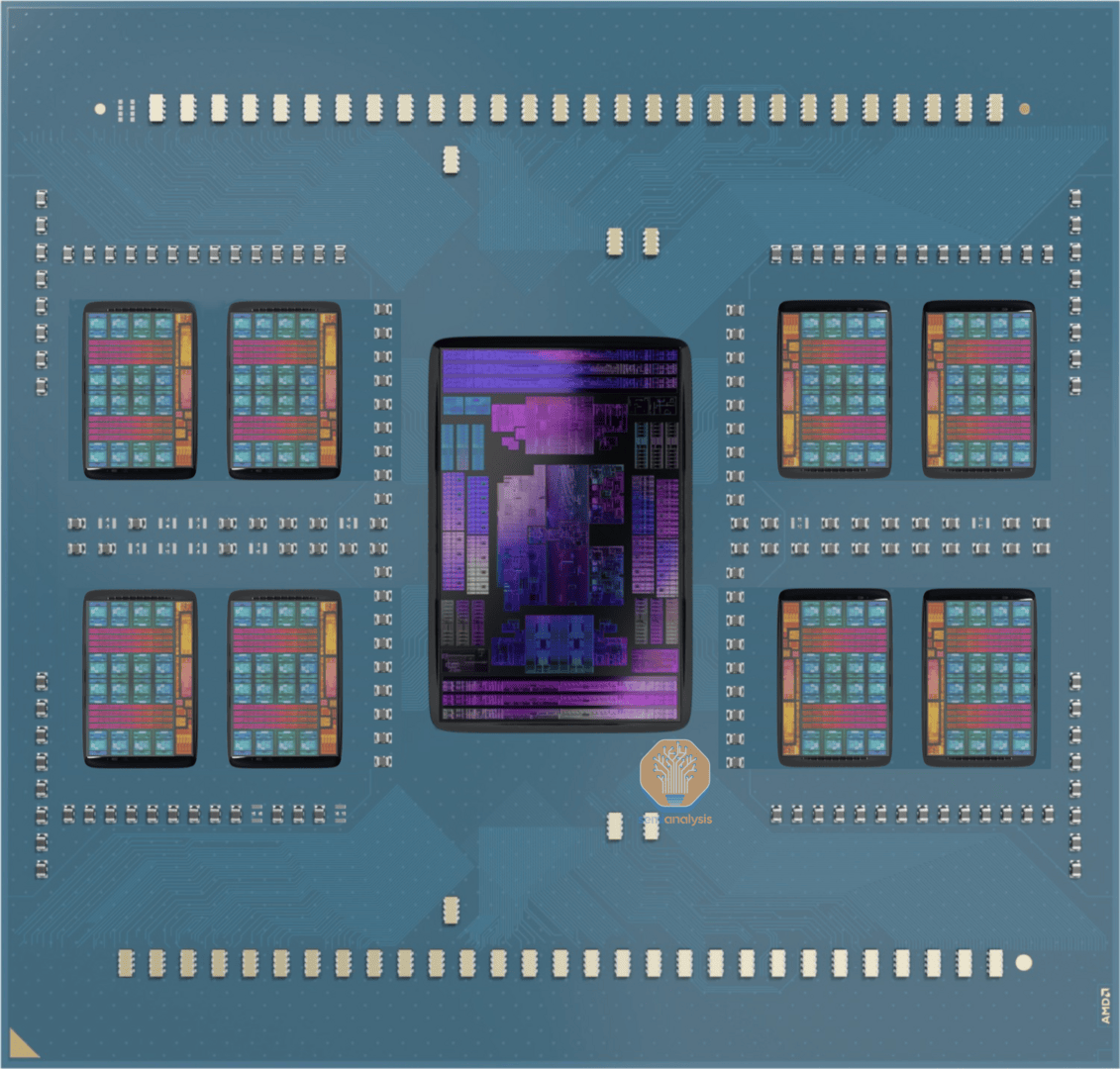

AMD combineert acht van deze kleine kernen met 16 MB L3-cache in een CCX en verbindt ze met andere CCX’s om een CCD te vormen. Acht van deze CCD’s zijn uiteindelijk terug te vinden op de Bergamo-processor, de I/O-chip in het midden is identiek aan die van Genoa, evenals alle parameters zoals geheugencontrollers, PCIe 5.0 en de rest. En dat is precies wat belangrijk is, want de software hoeft niet te worden aangepast en de SP5-processorsocket is volledig compatibel.

Uiteindelijk rijst de vraag of AMD niet gewoon 12 CCD’s in één pakket had kunnen bundelen, zoals Genua, om direct de 192-core Bergamo mogelijk te maken. Hier echter op dit moment niet, het pakket is nu de beperkende factor. Lessen uit de eerste generatie c-design worden echter snel geleerd, daarom zouden de reeds geraden 192 kernen in de Zen 5c mogelijk moeten zijn.

Bergamo zal naar verwachting deel uitmaken van “Datacenter en première van AI-technologieHet is gepresenteerd en recente geruchten hebben twee modellen bevestigd.

“Coffee fanatic. Gamer. Award-winning zombie aficionado. College student. Hardcore internet proponent. Twitter guru. Subtly charming bacon nerd. Thinker.”